mirror of

https://github.com/ByteByteGoHq/system-design-101.git

synced 2026-04-06 18:27:25 -04:00

This PR adds all the guides from [Visual Guides](https://bytebytego.com/guides/) section on bytebytego to the repository with proper links. - [x] Markdown files for guides and categories are placed inside `data/guides` and `data/categories` - [x] Guide links in readme are auto-generated using `scripts/readme.ts`. Everytime you run the script `npm run update-readme`, it reads the categories and guides from the above mentioned folders, generate production links for guides and categories and populate the table of content in the readme. This ensures that any future guides and categories will automatically get added to the readme. - [x] Sorting inside the readme matches the actual category and guides sorting on production

2.0 KiB

2.0 KiB

title, description, image, createdAt, draft, categories, tags

| title | description | image | createdAt | draft | categories | tags | |||

|---|---|---|---|---|---|---|---|---|---|

| Paging vs Segmentation | Explore paging vs segmentation: memory management techniques. | https://assets.bytebytego.com/diagrams/0269-memory-allocation-paging-vs-segmentation.png | 2024-03-05 | false |

|

|

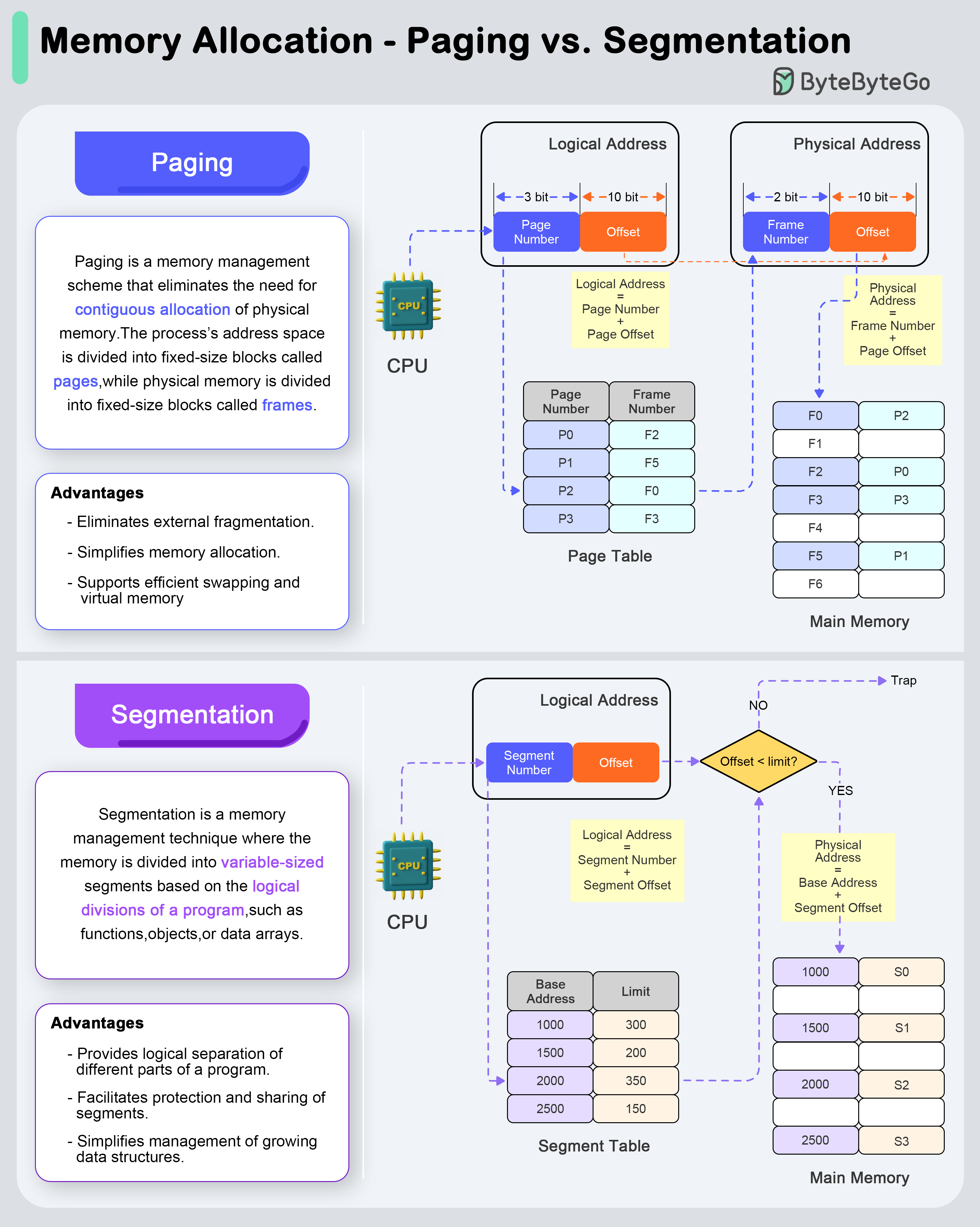

Paging

Paging is a memory management scheme that eliminates the need for contiguous allocation of physical memory. The process's address space is divided into fixed-size blocks called pages, while physical memory is divided into fixed-size blocks called frames.

The address translation process works in 3 steps:

- Logical Address Space: The logical address (generated by the CPU) is divided into a page number and a page offset.

- Page Table Lookup: The page number is used as an index into the page table to find the corresponding frame number.

- Physical Address Formation: The frame number is combined with the page offset to form the physical address in memory.

Advantages:

- Eliminates external fragmentation.

- Simplifies memory allocation.

- Supports efficient swapping and virtual memory.

Segmentation

Segmentation is a memory management technique where the memory is divided into variable-sized segments based on the logical divisions of a program, such as functions, objects, or data arrays.

The address tranlation process works in 3 steps:

- Logical Address Space: The logical address consists of a segment number and an offset within that segment.

- Segment Table Lookup: The segment number is used as an index into the segment table to find the base address of the segment.

- Physical Address Formation: The base address is added to the offset to form the physical address in memory.

Advantages:

- Provides logical separation of different parts of a program.

- Facilitates protection and sharing of segments.

- Simplifies management of growing data structures.